GPU芯片数字模块物理布局

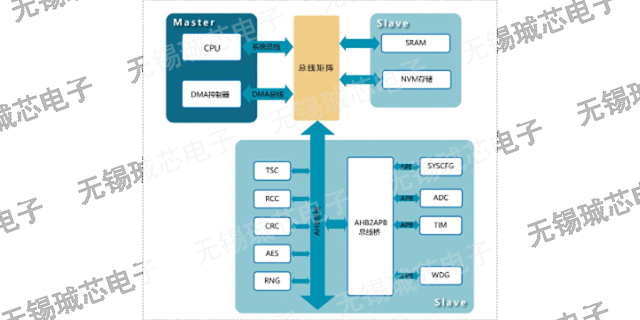

MCU的存储器MCU的存储器分为两种类型:非易失性存储器(NVM)和易失性存储器(SRAM)。NVM通常用于存储程序代码,即使在断电后也能保持数据不丢失。SRAM则用于临时存储数据,它的速度较快,但断电后数据会丢失。MCU的I/O功能输入/输出(I/O)功能是MCU与外部世界交互的关键。MCU提供多种I/O接口,如通用输入/输出(GPIO)引脚、串行通信接口(如SPI、I2C、UART)、脉冲宽度调制(PWM)输出等。这些接口使得MCU能够控制传感器、执行器和其他外部设备。芯片数字模块物理布局直接影响电路速度、面积和功耗,需精细规划以达到预定效果。GPU芯片数字模块物理布局

芯片设计的初步阶段通常从市场调研和需求分析开始。设计团队需要确定目标市场和预期用途,这将直接影响到芯片的性能指标和功能特性。在这个阶段,设计师们会进行一系列的可行性研究,评估技术难度、成本预算以及潜在的市场竞争力。随后,设计团队会确定芯片的基本架构,包括处理器、内存、输入/输出接口以及其他必要的组件。这一阶段的设计工作需要考虑芯片的功耗、尺寸、速度和可靠性等多个方面。设计师们会使用高级硬件描述语言(HDL),如Verilog或VHDL,来编写和模拟芯片的行为和功能。在初步设计完成后,团队会进行一系列的仿真测试,以验证设计的逻辑正确性和性能指标。这些测试包括功能仿真、时序仿真和功耗仿真等。仿真结果将反馈给设计团队,以便对设计进行迭代优化。贵州网络芯片设计流程高效的芯片架构设计可以平衡计算力、存储和能耗,满足多元化的市场需求。

可测试性是确保芯片设计成功并满足质量和性能标准的关键环节。在芯片设计的早期阶段,设计师就必须将可测试性纳入考虑,以确保后续的测试工作能够高效、准确地执行。这涉及到在设计中嵌入特定的结构和接口,从而简化测试过程,提高测试的覆盖率和准确性。 首先,设计师通过引入扫描链技术,将芯片内部的触发器连接起来,形成可以进行系统级控制和观察的路径。这样,测试人员可以更容易地访问和控制芯片内部的状态,从而对芯片的功能和性能进行验证。 其次,边界扫描技术也是提高可测试性的重要手段。通过在芯片的输入/输出端口周围设计边界扫描寄存器,可以对这些端口进行隔离和测试,而不需要对整个系统进行测试,这简化了测试流程。 此外,内建自测试(BIST)技术允许芯片在运行时自行生成测试向量并进行测试,这样可以在不依赖外部测试设备的情况下,对芯片的某些部分进行测试,提高了测试的便利性和可靠性。

现代电子设计自动化(EDA)工具的使用是芯片设计中不可或缺的一部分。这些工具可以帮助设计师进行电路仿真、逻辑综合、布局布线和信号完整性分析等。通过这些工具,设计师可以更快地验证设计,减少错误,提高设计的可靠性。同时,EDA工具还可以帮助设计师优化设计,提高芯片的性能和降低功耗。 除了技术知识,芯片设计师还需要具备创新思维和解决问题的能力。在设计过程中,他们需要不断地面对新的挑战,如如何提高芯片的性能,如何降低功耗,如何减少成本等。这需要设计师不断地学习新的技术,探索新的方法,以满足市场的需求。同时,设计师还需要考虑到芯片的可制造性和可测试性,确保设计不仅在理论上可行,而且在实际生产中也能够顺利实现。芯片架构设计决定了芯片的基本功能模块及其交互方式,对整体性能起关键作用。

传感器芯片是另一种重要的芯片类型,它们在各种检测和测量设备中发挥着关键作用。传感器芯片能够将物理量(如温度、压力、光线等)转换为电信号,为自动化控制系统提供必要的输入。随着物联网(IoT)的兴起,传感器芯片的应用范围越来越,从智能家居到工业自动化,再到环境监测,它们都是不可或缺的组成部分。 通信芯片则负责处理数据传输和通信任务。它们在无线网络、移动通信、卫星通信等领域扮演着重要角色。随着5G技术的推广和应用,通信芯片的性能和功能也在不断提升,以支持更高的数据传输速率和更复杂的通信协议。芯片前端设计主要包括逻辑设计和功能验证,确保芯片按照预期进行逻辑运算。湖南网络芯片设计流程

芯片数字模块物理布局的自动化工具能够提升设计效率,减少人工误差。GPU芯片数字模块物理布局

芯片技术作为信息技术发展的重要驱动力,正迎来前所未有的发展机遇。预计在未来,芯片技术将朝着更高的集成度、更低的功耗和更强的性能方向发展。这一趋势的实现,将依赖于持续的技术创新和工艺改进。随着晶体管尺寸的不断缩小,芯片上的晶体管数量将大幅增加,从而实现更高的计算能力和更复杂的功能集成。 同时,为了应对日益增长的能耗问题,芯片制造商正在探索新的材料和工艺,以降低功耗。例如,采用新型半导体材料如硅锗(SiGe)和镓砷化物(GaAs),可以提高晶体管的开关速度,同时降低功耗。此外,新型的绝缘体上硅(SOI)技术,通过减少晶体管间的寄生电容,也有助于降低功耗。GPU芯片数字模块物理布局

上一篇: 安徽射频芯片行业标准

下一篇: 广东GPU芯片数字模块物理布局